CMOS 회로의 사양은 대표적으로 fan-in 과 fan-out 을 들어 말할 수 있다.

각각의 정의는 다음과 같다.

fan out: 게이트 출력 단에 한번에 접속시켜 구동 가능한 최대 입력 수

fan in: 게이트 입력 단에 한번에 접속시켜 입력 가능한 최대 입력 수

[by 정보통신기술용어해설]

CMOS 에서는 몇개를 달던 동작은 한다.

하지만, 많이 접속시킬수록 Capacitor의 수는 많아질 것이고,

시상수가 커짐에 따라 Propagation Delay 가 커질 것이다.

우선 게이트가 병렬로 접속된 상태부터 살펴보면,

Propagation delay는 게이트의 개수에 비례하여 커진다는 것을 확인할 수 있다.

하지만 문제는,, 직렬접속에서 발생한다

게이트마다 드레인단에 달려있는 기생cap 들이 순차적 방전을 해버릴 수도 있다는 것이다.

만약 A의 입력신호가 제일 마지막에 들어온다면 이와 같은 상황이 발생한다.

C,B가 켜짐에 따라 각 nmos의 소스단의 전압은 Vdd가 되고, 각각의 Parastic cap을 충전시킨다.

마지막으로 A 게이트가 켜지면,

A의 소스-드레인단에 채널이 형성되어 Cpa가 방전되고

이후 순차적으로 Cpb Cpc Vout이 0이 된다.

이 문제를 해결하기 위해서는 Critical path 설계를 통해 가장 마지막에 신호가 들어오는 게이트를 출력단에 가까이에 배치하는 방법을 이용한다.

즉 마지막 게이트가 켜지기 전까지 전까지 GND쪽의 모든 Cap이 방전될 수 있도록 하는 것이다.

GND에 가장 가까운 회로부터 방전할때의 tp를 생각해보면 N번째 cap 방전까지 저항이 하나씩 더해진다는 것을 확인할 수 있다.

N번째 cap방전시에는 1~N번 게이트를 모두 지나 방전하게 되므로

(R1+R2+....+RN)Cpn.

어쨋든 출력 단이 0이 되기 위해서는 모든 cap들이 방전 되어야 한다.

C1 방전시 지나는 gate 수=1

C2 방전시 지나는 gate 수=2

C3 방전시 지나는 gate 수=3

..

CN 방전시 지나는 gate 수=N

1+2+3+...+N=N(N+1)/2

tp는 N(N+1)/2 에 비례하여 증가하게 된다.

앞서 병렬로 연결한 gate에서의 tp는 게이트의 개수에 비례하려 증가하고, 직렬로 연결한 gate에서는 exponential 하게 증가한다고 설명하였다.

이를 통해 NOR와 NAND cmos inverter를 설계해보면 다음과 같다.

여기서 주목할 점은,

안그래도 저항이 큰 pmos를 직렬로 연결해버리면 tp도 exponential 하게 증가해버리는 최악의 상황이 발생한다는 것이다.

따라서, pmos의 직렬연결을 어떻게든 피하는 것이 좋다.

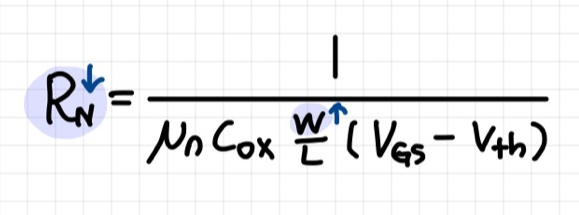

이쯤에서 W를 키워 R의 크기를 줄이는 방법에 대해서도 생각해 볼 수 있다.

W가 커지면, R은 작아진다.

하지만..

W가 커지면 C도 커진다

tp를 줄이기 위해 W를 늘린거였으나

결국 R과 C가 trade off 관계가 되어버렸다.

그래도 최대한 W를 늘릴 수 있는 방법으로써 제시된 방법은 이와 같다.

Cap들이 방전될때 첫번째 Gate는 모두 지나간다.

따라서, 가장 많이 지나가는 첫번째 nmos의 W를 키운다.

다음으로 많이 지나가는 R2, R3,.. 은 점점 W를 줄여가며 Gate의 W에 차이를 두어 설계하는 방법이다.

(참,, 똑똑하다)

nmos inverter 은 Output Low일때 회로가 전압분배기처럼 작용하여 Vol이 완전히 0이 되지 않아 static 전력이 발생하는 등 단점이 많았다.

따라서 각 mos를 독립적으로 제어할 수 있는 CMOS inverter을 사용하게 되었는데,

CMOS에서는 트랜지스터가 직렬로 접속되는 상황을 피할 수가 없다.

단점만 있는 줄 알았던 nmos inverter도 CMOS 보다 나은 점이 있었다!

- 게이트의 직렬 연결 피할 수 있음

- 사용하는 트랜지스터 수 N+1 (PDN+PUN)

c.f. # of transistor in CMOS=2N

(동일한 개수의 PDN과 PUN)

Pseudo nmos inverter 은

N개의 nmos와 Gate가 접지된 1개의 pmos로 구성되어있다.

댓글